# **Vertical Germanium Nanowire Arrays in Microfluidic Channels for Charged Molecule Detection**

Makoto Koto, Paul W. Leu, and Paul C. McIntyre\*

Department of Material Science and Engineering, Stanford University, Stanford, California 94305, USA

We demonstrate the fabrication of vertical germanium nanowire (Ge NW) molecular sensor arrays that are suitable for biological field-effect-transistor sensing, using conventional semiconductor fabrication processes. The proposed fabrication process enabled production of freestanding vertical NW arrays with a Schottky junction top contact. The arrays' dc current–voltage characteristics could be modulated by altering the solution pH in contact with the HfO<sub>2</sub> gate insulator-coated nanowire surface. A sensitivity of 50 nS/pH with 1  $\mu$ m<sup>2</sup> sensor area is demonstrated for undoped vertical Ge NW arrays. © 2008 The Electrochemical Society. [DOI: 10.1149/1.3033522] All rights reserved.

Manuscript submitted July 16, 2008; revised manuscript received October 13, 2008. Published December 9, 2008.

One-dimensional devices such as semiconductor nanowires (NWs), have attracted much interest because of their unique characteristics. Previous studies have shown the potential of NWs for interconnects, field-effect transistors (FETs), <sup>1,2</sup> and sensors. <sup>3</sup> For sensor device applications, several authors have reported on NW-based devices in which a very high sensitivity is obtained by the selective binding of molecules to the wire surface, thus inducing charge transfer and a conductance change in the wire. However, in previous research, NWs were first removed from their host substrate, collected in solution, and finally deposited onto another substrate. Therefore, most NW-based devices reported to date sit horizontally on the substrate. From the fluid dynamics viewpoint of target molecule capture and detection in solution, freestanding FET structures are preferable, as the amount of NW surface exposed to the fluid is increased and the functionalized NW surface region at which molecules bind can be far away from the solution/fluidic channel boundary layer across which molecules must, in the absence of convection or stirring, diffuse to reach the wire surface. In addition, an enhanced electrolyte-insulator-semiconductor capacitance is expected for freestanding, "surround-gate" channel structures.

In the present research, we have demonstrated reproducible pH sensing using vertical, freestanding Ge NW devices fabricated within a microfluidic channel on a Si(111) wafer. Furthermore, the Au catalyst particles at the tips of the NWs were removed during the fabrication process, which may improve its adaptation to a conventional semiconductor process. Because of its conventional processes to fabricate the sensor array, the devices can be easily reproduced with a reliable sensing performance.

#### **Experimental**

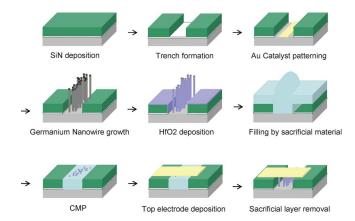

Figure 1 shows an overview of the fabrication process. A lowresistivity silicon substrate served as the common bottom electrode for the NW array sensors. The substrate used in this study was As-doped silicon (111) with 0.05–0.09  $\Omega$  cm resistivity. To fabricate microfluidic channels, 140 nm silicon oxide and 860 nm silicon nitride were formed by furnace oxidation and chemical vapor deposition (CVD), respectively. The silicon dioxide film functioned as an etch stop layer during silicon nitride dry etching and as a buffer layer between the silicon substrate and the relatively higher-stress silicon nitride. The silicon nitride film formed by low-pressure CVD on silicon substrates can cause high biaxial stresses of +850 MPa (compressive) to -300 MPa (tensile) in the silicon substrate. Therefore, thermal silicon oxide was used to reduce the interfacial stresses and improve the adhesion between the silicon nitride and silicon substrate. Growth and deposition of the oxide and nitride layers was followed by optical lithography and dry etching of the silicon nitride. To etch the silicon nitride, we used a SF<sub>6</sub> flow of 100 sccm and an  $\mathrm{O}_2$  flow of 10 sccm, and a total pressure of 150 mTorr gas plasma with 150 W radio-frequency (rf) power. This etched the silicon nitride at about 90 nm/min. The underlying silicon dioxide also served as an etch stop layer to prevent dry etching damage to the silicon surface, which is important for epitaxial NW growth. After nitride etching, the remaining thermal oxide was removed by 5 min of exposure to 6:1 buffered oxide etch, which comprises a 6:1 volume ratio of NH<sub>4</sub>F to HF. For subsequent NW nucleation and epitaxial growth from the Si surface, it is desirable to have minimal surface damage during oxide etching and, therefore, we applied wet etching for this process step. After these processes, a 10-200 µm width and 1 µm depth microfluidic channel with circular wells at both of its ends was formed. Before Au NW catalyst deposition, the samples were exposed to O2 plasma, which was produced by 150 W rf power plasma with an O2 flow of 100 sccm and a pressure of 150 mTorr for 2 min to remove postetch contamination. Thereafter, the samples were dipped in 50:1 deionized water:HF acid solution for 1 min to remove native oxide from the Si(111) surface. Then, a Au film of 5 nm thickness was deposited as a catalyst for vaporliquid-solid (VLS) NW growth by dc Ar sputtering in a system with a base pressure of 10<sup>-6</sup> Torr. The Au was sputtered by ionized Ar in a plasma produced by 75 W dc power supply at room temperature and deposited on a sample piece placed on the electrically ground connected cathode plate. The sputtering rate was 35 nm/min.

Next, the sample was loaded into the NW reactor via an argonpurged load lock with a base pressure of  $10^{-6}$  Torr. The Ge NWs were grown by the VLS mechanism using a lamp heated, cold wall CVD system. The mixture of hydrogen and germane was introduced into the reactor at a total pressure of 30 Torr. The partial pressure of germane was 0.5 Torr. The samples were heated up to the nucleation temperature (350°C) and held at that temperature for 2 min, and then were lowered to the growth temperature (300°C) for 18 min of growth under deep subeutectic VLS conditions. <sup>7,8</sup> As previously re-

Figure 1. (Color online) Schematic of vertical freestanding NW fabrication process.

<sup>\*</sup> Electrochemical Society Active Member.

<sup>&</sup>lt;sup>z</sup> E-mail: mkoto@stanford.edu

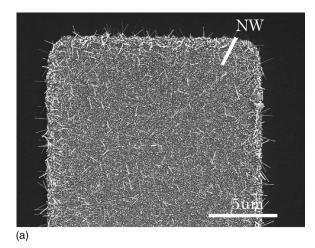

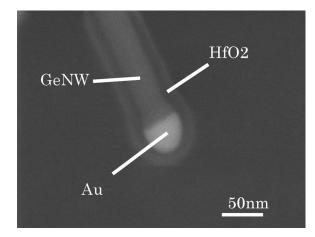

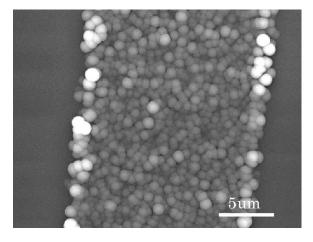

**Figure 2.** Results from Ge NW growth from lithography patterned Au film. (a) Plan-view SEM image of Ge NW array. (b) Cross-section SEM image of Ge NWs. The perpendicular direction corresponds to Si[111].

ported, for a CVD growth environment that is relatively free of impurities such as oxygen, this two-temperature growth procedure gives less tapered Ge NWs than does Ge NW growth at a single temperature at which nucleation occurs readily on the (111) substrate surface.

Figure 2a shows a plan-view scanning electron microscope (SEM) image of NWs grown from the Au catalyst film in the microfluidic channel. During heating to the NW nucleation temperature, the thin Au film becomes discontinuous and individual NWs nucleate from the resulting Au catalyst nanoparticles on the Si(111) surface. From the SEM observation results, the average nanowire diameter was calculated as 40 nm. The Ge NW growth region within the channel was well-defined by the area of the lithographically patterned Au catalyst film. As shown in Fig. 2b, little sidewall taper was observed for Ge NWs deposited by the two-step temperature nucleation and growth process. Most of the wires appear to grow along either the vertical or inclined (111) axis of the substrate, consistent with epitaxial Ge NW growth. The areal density of NWs grown as a fabricated sensor array within a microfluidic channel was roughly 1 NW/μm<sup>2</sup>. To obtain a higher density nanowire array, we can modulate growth conditions; nucleation temperature and growth temperature, as previously reported.8

Following NW growth, samples were coated with a 5 nm  $HfO_2$  film by atomic layer deposition (ALD) using sequential pulses of tetradiethyl amido hafnium precursor and water vapor oxidant at  $150^{\circ}C$  substrate temperature. Before  $HfO_2$  ALD, the Ge-coated sample surface was treated for  $150 \, \text{s}$  using a remote inductively coupled plasma generated using an inlet gas mixture of  $Ar/N_2/H_2$ :

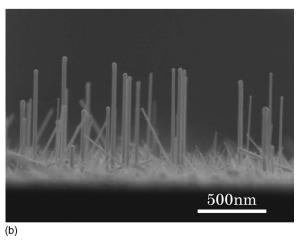

Figure 3. Cross-section SEM image of a single Ge NW coated by a 5 nm thick layer of  $HfO_2$  deposited by ALD.

$1000/80/10~\rm sccm$  at 420, to produce a thermally stable surface layer which is expected to have a lower density of interfacial traps than the native oxide of Ge.  $^{9,10}$  The  $HfO_2$  film subsequently underwent an additional in situ high-temperature annealing step in the ALD chamber to improve its relative density and chemical resistance to subsequent processing steps and aqueous solution exposure. The anneal gas, temperature, and time were  $N_2$  10 sccm, 420°C, and 1 h, respectively.

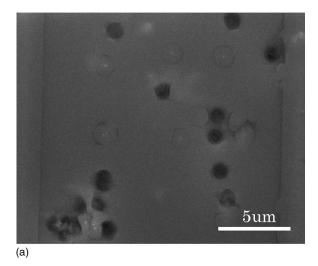

Figure 3 shows that the deposited ALD HfO<sub>2</sub> layer uniformly covers the Ge NWs. As reported previously, <sup>11</sup> the postdeposition annealing of the HfO<sub>2</sub> film makes it chemically resistant to dilute hydrogen fluoride exposure during wet etching of the sacrificial plasma-enhanced chemical vapor deposition (PECVD) grown SiO<sub>2</sub> encapsulation. Therefore, the HfO<sub>2</sub> layer functions both as an etch stop and as a high-permittivity gate insulator for the Ge NW biological-FET sensors. To confirm the tolerance of the ALD HfO<sub>2</sub> film to dilute hydrogen fluoride solution, we performed SEM observation of HfO<sub>2</sub>-coated Ge nanowires after removal of the sacrificial PECVD-grown SiO<sub>2</sub>. No evidence of damage to the nanowires during PECVD oxide etching and subsequent sample drying was observed. A sacrificial PECVD silicon dioxide with 1.4 μm nominal thickness was then deposited to fill the microfluidic channel. A planview image of the conformal plasma CVD oxide covering the Ge NWs in the microfluidic channel is shown in Fig. 4.

To expose the NW tips, the sample was planarized by chemical-mechanical polishing (CMP).  $^{12}$  In general, polishing of SiO<sub>2</sub> is quite

Figure 4. Plan-view SEM image of the sacrificial PECVD  ${\rm SiO_2}$  layer deposited onto the Ge NW array.

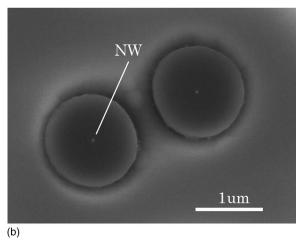

**Figure 5.** SEM image showing two magnifications of the CMP polished surface where the Ge NW tips are exposed.

selective over  $\mathrm{Si_3N_4}$ , enabling the silicon nitride film to be used as a stop layer during the CMP process. <sup>13</sup> This also helps to obtain uniform vertical NW lengths in the microfluidic channel. The exposed NW tip cross sections after CMP are shown in Fig. 5. As a general compatibility issue for semiconductor devices, Au is soluble in Si and produces a deep carrier trap state which acts as an efficient generation/recombination center, thus reducing the minority carrier lifetime and increasing p-n junction leakage. <sup>14</sup> In our fabrication process, the Au particles on the Ge NW tip can be removed by CMP because the NWs are grown longer than the trench depth. As the Au catalysts stay on the top of the NWs during VLS growth, they can be removed during the CMP process.

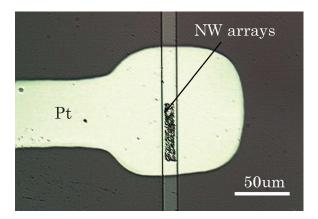

A common top electrode for each NW sensor array was formed by depositing a metal layer on the exposed NW tips. Optical microscope images in Fig. 6 illustrate that the sputtered top platinum contact of 100 nm thickness covers the NW growth region completely. We also evaluated Pd and Cr as a top electrode metal. The contact area was defined by metal sputter deposition through a shadow mask. By subsequently removing the trench-filling sacrificial layer, vertical, freestanding Ge NW arrays were obtained inside the microfluidic channel. The trench-filling sacrificial layer was removed by dipping in buffered HF acid (mixture of HF acid and ammonium fluoride with a ratio of 6:1) for 20 min.

Electrical measurements were performed with a Keithley 6512 programmable electrometer and Keithley 230 programmable voltage source operated by Lab-View software in a semiconductor probe

**Figure 6.** (Color online) Plan-view optical microscope image of Pt electrode deposition through a shadow mask on the Ge NW growth region, inside the microfluidic channel.

station. A solution of varying pH and phosphate buffer solution was syringe-injected into the NW array via the microfluidic channel.

#### **Results and Discussion**

From SEM observation after nanowire growth, we confirmed that, in addition to the vertical  $\langle 111 \rangle$  Ge NWs, unreacted Au particles and epitaxial nanowires growing parallel to the inclined  $\langle 111 \rangle$  axes of the Si(111) substrate were present on the sample surface. The unreacted Au particles cannot be removed by the CMP used to planarize the sensor array, and may cause degradation of the NW sensor performance. As demonstrated recently, however, it is possible to remove the Au with reasonable selectivity by wet etching after NW growth,  $^{15}$  and this technique could be applied in the future to mitigate the effects of the residual Au.

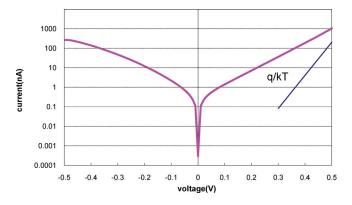

Integration of a high-*k* HfO<sub>2</sub> gate dielectric layer in NW FETs results in promising device characteristics. <sup>16</sup> The current–voltage behavior of the vertical Ge NW biosensor array fabricated in the present work, before removal of the sacrificial PECVD oxide encapsulation, is shown in Fig. 7. Voltage was applied between the source (heavily doped Si substrate) and drain (Pt electrode) contacts of these undoped and ungated vertical NWs. To normalize the current data, the current values are divided by the estimated number of NWs, as observed by SEM imaging, beneath the top electrode.

The current measured across the NW array has a nonlinear dependence on applied voltage, indicating the presence of a potential barrier to charge transport. Unlike previously reported<sup>1,2</sup> work on

**Figure 7.** (Color online) Normalized logarithmic scale current–voltage characteristics of vertical freestanding Ge NW. The current values shown in these graphs are divided by the estimated number of NWs per pad.

**Figure 8.** Schematic of energy band profile of vertical Ge NW device at (a) positive bias and (b) negative bias.

symmetric metal/semiconductor contacts, our NW devices exhibit an asymmetric current–voltage characteristic as a consequence of the asymmetry of the electrode structure.

For Pt/(111) Ge contacts, the Fermi level is reported to be pinned at an energy close to the valence bandedge. <sup>17</sup> Because our Ge NWs are undoped and close to intrinsic, a Schottky barrier of  $\sim\!0.67$  eV is created at the Pt and Ge interface. This barrier would be expected to affect dc carrier transport across the Ge NW array. We found that the current–voltage characteristics of Pt, Pd, and Cr electrodes, which have vacuum workfunctions that span the range 4.5–5.6 eV, were similar. This indicates that the Fermi level of the metal/Ge NW interface was strongly pinned.

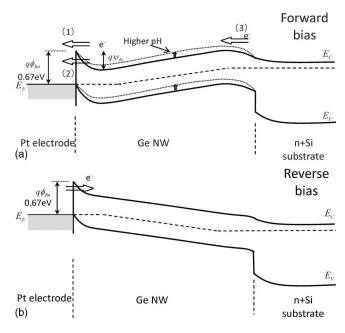

At positive bias to the top Pt electrode (forward bias to the Schottky junction), considering the expected energy band diagram for our NW device with strong Fermi energy pinning at the Pt contact interface, the observed current density-voltage characteristics may result from a combination of (1) thermionic emission across the Pt/Ge NW interface or (2) a parallel leakage path at the Pt/Ge NW interface, or (3) the electron diffusion current from the n + Si bottom contact into the GeNW, as shown in Fig. 8a. Here, thermionicfield emission and field-emission components are expected to be negligible because the semiconductor doping is low in our NW devices, implying a very small population of conduction electrons which could tunnel into the metal electrode under forward bias. Because the dc current across the NW sensors varies in proportion to the exponential of the applied bias, the current is mainly determined by Fig. 8a(1) Schottky thermionic emission, the current of which is given by

$$J = Js0[\exp(qVds/kT) - 1] \quad Js0 = A*T^2 \exp(-q\phi_{Bn}/kT)$$

where A is the Richardson constant,  $\phi_{Bn}$  is barrier height for electrons, k is Boltzmann's constant, and T is absolute temperature, or Fig. 8a(2) the diffusion current, which is given by

$$J = Js1[\exp(qV/kT) - 1]$$

where Js1 is saturation current density at a junction of n+Si and Ge NW. The current density data at a bias of +0.2 to 0.3 V on the top Pt electrode shown in Fig. 7 scale with voltage in proportion to qV/nkT, where n, the ideality factor, is 2.8. In the case of current limited by ideal thermionic emission at the Schottky junction formed by the Pt/Ge contact Fig. 8a(1), n should be approximately

equal to 1. If the current is limited by minority carrier diffusion across the junction between the Ge NW and  $n + \mathrm{Si}$  substrate, n should be in the range of 1 (thermal emission dominates) to 2 (carrier generation–recombination dominates). This indicates that another component for current flow across the NW array has to be considered besides mechanism Fig. 8a(1) thermionic emission or mechanism Fig. 8a(3), the drift current or the generation–recombination. As previously reported,  $^{19,20}$  a continuous distribution of surface states related to this contact interface is expected in the Ge bandgap. In addition to these surface states, we expect that defects form on the GeNW surface as a result of the polishing and other process steps used in NW sensor array fabrication. Tunneling assisted by the presence of these surface states/defects can cause a parallel leakage path, and this may contribute to a larger ideality feature.

At negative bias to the top Pt electrode (reverse bias to the Schottky junction), the energy band profile becomes more sensitive to Fig. 8a(2) parallel leakage current across the Pt/Ge contact as shown in Fig. 8b because the width of the Schottky barrier is decreased by the negative applied voltage on the top Pt electrode. As the bias becomes increasingly negative, the current increases gradually and a much higher current value than that of an ideal Schottky reverse biased junction (< nA per wire based on reasonable assumed values for the electronic properties of the various materials and interfaces) is observed. Because the built-in potential  $\psi bi$ , which is shown in Fig. 8a, is approximately 0.34 eV at thermal equilibrium for the undoped Ge NW, current flow by nonthermionic, surface/ defect states-assisted tunneling can contribute in this experiment's range of applied bias ( $\pm 0.3$  V). This should produce a gradual dc current increase across the NW device as the magnitude of the negative bias increases. <sup>21,22</sup> The defect-assisted tunneling current is proportional to the integral of the tunneling probability, which is not thermally activated. <sup>23</sup> Consistent with this, the current–voltage characteristics for negative bias on the top Pt electrode do not show an exponential increase with applied voltage, unlike the positive bias case.

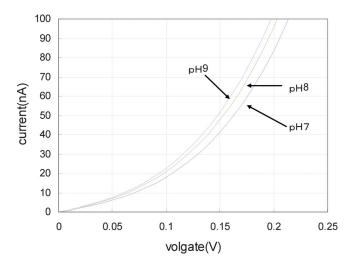

As for device stability for the removal process of the sacrificial layer, the difference of current–voltage characteristics between before and after removal was negligible. The freestanding Ge NWs arrays were immersed in aqueous solutions with pH ranging from 7 to 9. Figure 9a shows the dependence of dc conductance on pH for +0.2 V bias. The isoelectric point of HfO<sub>2</sub> is pH  $7.1;^{24}$  therefore, solution pH larger than this value will result in a higher concentration of negative charge on the hafnium oxide surface, and a resulting surface band bending in the semiconductor nanowire as shown in Fig. 8a.

From the current-voltage behavior of the fabricated vertical Ge NW sensor array before removal of the sacrificial PECVD oxide encapsulation, as discussed in the previous section, we cannot distinguish unambiguously which conduction mechanism is dominant. However, considering the expected Schottky barrier height of 0.67 eV for electrons at the Pt contact/Ge NW interface, the expected conduction band-edge difference of 0.1 eV at the Ge NW/n + Si substrate interface, which is estimated from  $E_C-E_F$ where  $E_{\rm C}$  is conduction band-edge,  $E_{\rm F}$  is Fermi level of Ge NW and Si  $n^+$  substrate calculated by doping concentration, <sup>25</sup> the upward band bending in the NW with increasing pH, and the observed current increase at higher pH under positive bias to the Pt electrode, we can conclude that the Pt/Ge NW interface Schottky junction dominates the current-voltage behavior of the device during sensing. We measured a sensitivity of 50 nS/per unit pH at a positive bias to the top Pt electrode of 0.2 V.

The reversibility of the pH sensing measurement was confirmed, as shown in Fig. 9b. After changing the solution using a syringe, the conductance was measured immediately. The response time for the conductance change was <10 s, and is believed to be dictated by the rate of flow through the microfluidic channel. Through several

**Figure 9.** (Color online) Vertical Ge NWs sensor array pH sensing results: (a) conductance dependence for pH and (b) conductance reversibility as a function of pH. The top electrode was biased at +0.2 V.

measurements of pH, we did not notice any conspicuous change of the current–voltage characteristics. This indicates the stability and robustness of the fabricated device.

As compared with previous work, the pH change for the present vertical NW devices resulted from changes in Schottky-barrier limited current. The previous work measured carrier accumulation in a normally on metal-oxide-semiconduct field-effect transistor in which the conductance is proportional to  $\mu$  CV, where  $\mu$  is the carrier mobility and C is the channel capacitance. Thus, it is difficult to compare the results quantitatively because the current transport mechanisms, semiconductor material, and doping concentration differ. However, we obtained the same order of magnitude conductance change (50.0 nS/pH) with a 1  $\mu m^2$  sensor area as in previously reported pH sensing experiments using NW-based devices  $(100 \pm 20 \text{ nS/pH})$ . This may result from the comparable dc conductance of NWs for the measurement conditions used. The previously reported pH sensing devices consisted of NWs in which the conductance (dI/dVg) was approximately 500–2000 nS.<sup>3</sup> The normalized conductance (dI/dVd) of the Ge NWs in our sensor arrays at +0.2 V is 109 nS. For our devices, the Schottky-limited dc conductance is very sensitive to the drain bias voltage. For instance, the experimentally measured NW conductance at +0.3 and +0.4 V is 526 and 2810 nS, respectively. Thus, we can anticipate larger conductance changes and higher sensitivity by optimizing the drain voltage for our devices. We can also improve the sensitivity by increasing the sensor area size.

From the viewpoint of comparison with recently reported ion sensitive FETs (50–60 mV/pH), <sup>26,27</sup> our device achieved the same order of magnitude of sensitivity (12 mV/pH), as shown in Fig. 10.

Figure 10. (Color online) The current-voltage characteristics' dependency on solution pH.

# Conclusions

Sensor devices composed of vertical Ge NW arrays which function as FET channels have been fabricated by conventional semiconductor fabrication processes in a microfluidic channel on silicon. A conformal  $HfO_2$  film deposited by ALD around the Ge NWs functioned as a gate insulator and etch stop layer for the sacrificial oxide encapsulation, which was removed to provide freestanding vertical NWs. The  $HfO_2$  layer also contributes to accurate and sensitive detection by increasing the effective capacitance density of the NW devices. The Au catalyst for low-temperature VLS NW growth was removed from the NW tips during sensor array planarization.

As compared with previously reported pH sensing results using NW-based devices, we demonstrated a comparable conductance change of 50.0 nS/pH, which was anticipated from the differences of carrier transfer with 1  $\mu m^2$  sensor area. Experimental results indicate that our device's current–voltage characteristics are dominated by the presence of a Schottky barrier between the undoped Ge NW and metal top contact; however, pH changes were effective in modulating the wire conductance.

# Acknowledgments

The authors thank the members of Nanowire Growth Facility at Stanford University; Dr. Joshua Ratchford, Irene Goldthorpe, Yuan Zang for helpful discussions, and Dr. James McVittie, Professor Christopher E. D. Chidsey, and Professor Yoshio Nishi for managing the facility.

Stanford University assisted in meeting the publication costs of this article.

### References

- 1. Y. Cui, X. Duan, J. Hu, and C. M. Lieber, J. Phys. Chem. B, 104, 5213 (2000).

- 2. S. W. Chung, J. Yu, and J. Heath, Appl. Phys. Lett., 76, 2068 (2000).

- 3. Y. Cui, Q. Wei, H. Park, and C. M. Lieber, *Science*, **293**, 1289 (2001).

- P. R. Nair and M. A. Alam, Appl. Phys. Lett., 88, 233120 (2006).

R. Tu, L. Zhang, Y. Nishi, and H. Dai, Nano Lett., 7, 1561 (2007)

- A. Tarraf, J. Daleiden, S. Iremer, D. Prasai, and H. Hillmer, J. Micromech. Microeng., 14, 317 (2004).

- H. Adhikari, A. F. Marshall, I. A. Goldthorpe, C. E. D. Chidsey, and P. C. McIntyre, Nano Lett., 6, 318 (2006).

- H. Jagannathan, M. Deal, J. Woodruff, C. Chidsey, P. C. McIntyre, and Y. Nishi, J. Appl. Phys., 100, 024318 (2006).

H. Kim, P. C. McIntyre, C. O. Chui, K. C. Saraswat, and M. H. Cho, Appl. Phys.

- Killi, F. C. McIntyle, C. O. Chui, K. C. Saraswat, and M. H. Cho, *Appl. Phys. Lett.*, 85, 2902 (2004).

Y. Oshima, Y. Sun, D. Kuzum, T. Sugawara, K. C. Saraswat, P. Pianetta, and P. C.

- McIntyre, J. Electrochem. Soc., 155, G304 (2008).

V. Kaushik, M. Claes, A. Delabie, S. V. Elshocht, O. Richard, T. Conard, E. Rohr, T. Witters, M. Caymax, S. D. Gendt, et al., Microelectron. Reliab., 45, 798 (2005).

- P. W. Leu, H. Adhikari, M. Koto, K. H. Kim, P. Rouffignac, A. F. Marshall, R. G. Gordon, C. E. D. Chidsey, and P. C. McIntyre, *Nanotechnology*, 19, 485705

- 13. C. F. Lin, W. T. Tseng, M. S. Feng, and Y. L. Wang, Thin Solid Films, 347, 248 (1999).

- R. H. Hopkins and A. Rohatgi, J. Cryst. Growth, 75, 67 (1986).

J. H. Woodruff, J. B. Ratchford, I. A. Goldthorpe, P. C. McIntyre, and C. E. D. Chidsey, Nano Lett., 7, 1637 (2007).

D. Wang, Q. Wang, A. Javey, R. Tu, H. Kim, T. Krishnamohan, P. C. McIntyre, K.

- C. Saraswat, and H. Dai, *Appl. Phys. Lett.*, **83**, 2432 (2003).

T. Nishimura, K. Kita, and A. Toriumi, *Appl. Phys. Lett.*, **91**, 123123 (2007).

S. M. Sze, *Physics of Semiconductor for Devices*, p. 162, John Wiley & Sons, New March 1986. York (2003).

- R. H. Kingston, J. Appl. Phys., 27, 101 (1956).

T. Hanrath and B. A. Korgel, J. Phys. Chem., 109, 5518 (2005).

- 21. U. K. Mishra and J. Singh, Semiconductor Device Physics and Design, p. 228, Springer, Netherlands (2007).

- 22. J. Kotani, H. Hasegawa, and T. Hashizume, Appl. Surf. Sci., 237, 213 (2004).

- 23. K. Aflatooni, R. Hornsey, and A. Nathan, IEEE Trans. Electron Devices, 46, 1417 (1999).

- 24. M. Kosmulski, Langmuir, 13, 6315 (1997).

- 25. S. M. Sze, *Physics of Semiconductor for Devices*, p. 27, John Wiley & Sons, New York (2003).

- 26. W. Y. Chung, C. H. Yang, D. G. Pijanowska, P. B. Grabiec, and W. Torbicz, Sens. Actuators B, 113, 555 (2006).

- 27. T. Sakata, M. Kamaharoi, and Y. Miyahrara, Jpn. J. Appl. Phys., Part 1, 44, 2854 (2005).